# CENG 311 Computer Architecture

#### Lecture 1

# Introduction to Computer Architecture

Asst. Prof. Tolga Ayav, Ph.D.

Department of Computer Engineering İzmir Institute of Technology

#### **Computer Design**

#### **Instruction Set Design**

- Machine Language

- Compiler View

- ° "Computer Architecture"

- "Instruction Set Processor"

"Building Architect"

#### Computer Hardware Design

- ° Machine Implementation\

- ° Logic Designer's View

- "Processor Architecture"

- ° "Computer Organization"

"Construction Engineer"

Few people design computers! Very few design instruction sets! Many people design computer components.

Very many people are concerned with computer function, in detail.

## The Big Picture

- What is inside a computer?

- How does it execute my program?

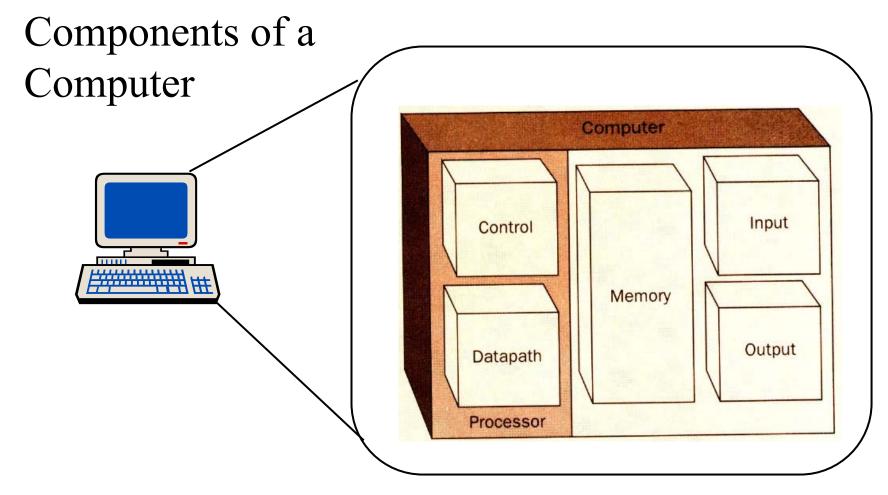

## The Big Picture

• The Five Classic

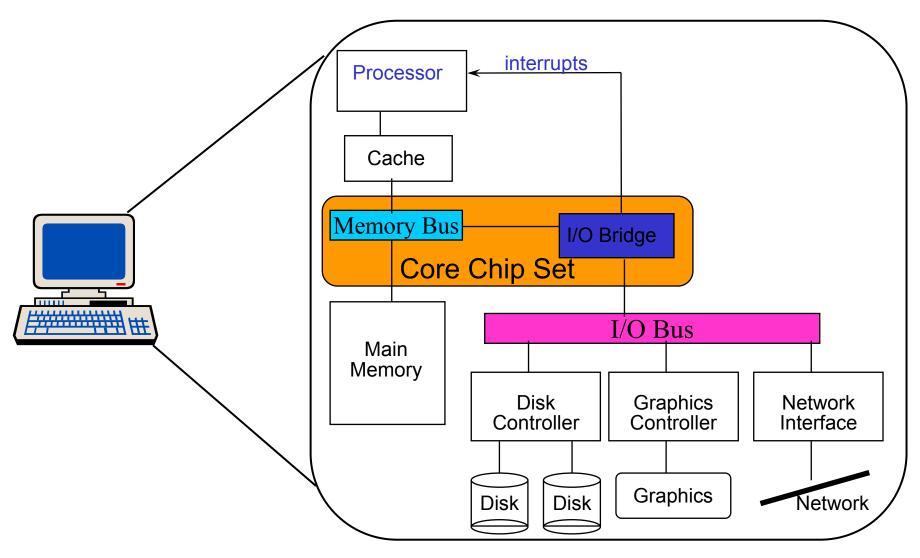

## System Organization

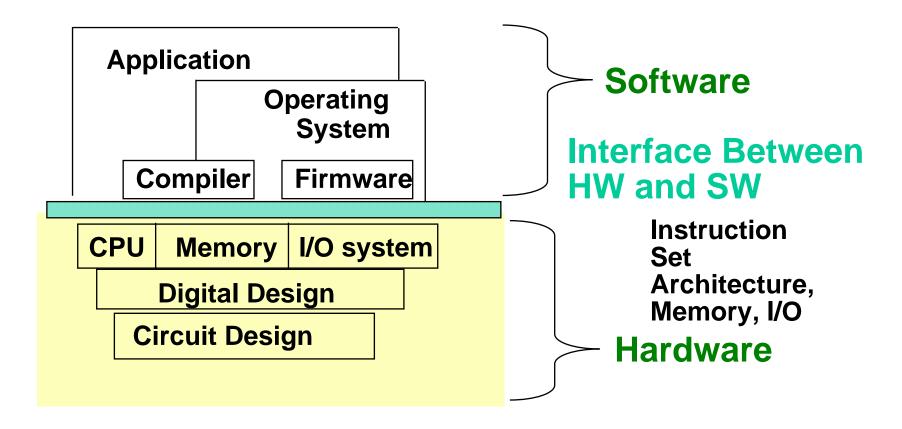

# What is Computer Architecture?

Coordination of levels of abstraction

Under a set of rapidly changing Forces

## Levels of Representation

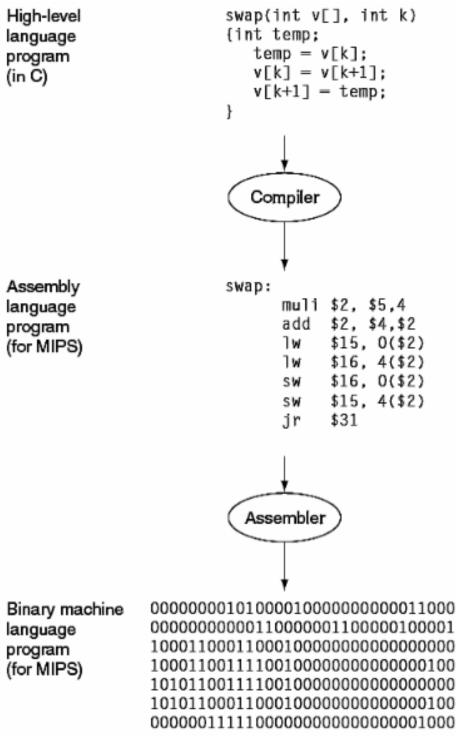

temp = v[k]; **High Level Language Program** v[k] = v[k+1];v[k+1] = temp;Compiler lw \$15, 0(\$2)**Assembly Language** 4(\$2) lw \$16, **Program** sw \$16, 0(\$2)**Assembler** sw \$15, 4(\$2) **Machine Language** 0110 1010 1111 0000 1001 1000 1100 0110 **Program** 1010 0101 1000 0000 1001 1001 1100 0110 0000 **Machine Interpretation** RegDst Don't Care ALUctr MemtoReg **Control Signal** Rw Ra Rb busW **Specification** Registers Memory

İzmir Institute of Technology

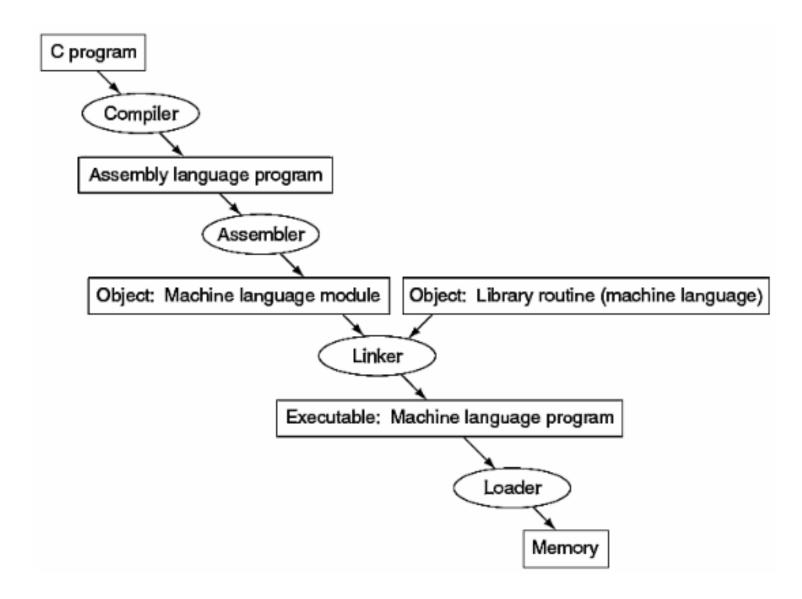

#### Compiler-Assembler

## Translation hierarchy for C

### **Basic Elements**

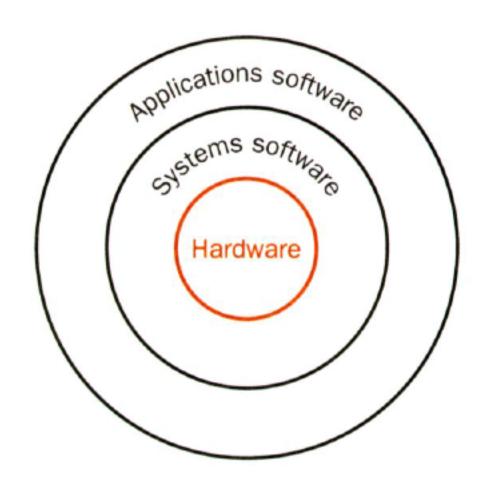

#### **Functional Levels:**

- Application LayerSystem SoftwareHardware Layer

### MIPS Assembly

- move \$t0, \$t1

- add \$t0, \$zero, \$t1

- sll \$t1, \$a1, 2 (reg <math>t1=k\*4)

- lw \$t0=4(\$t1) (reg \$t0=v[k+1])

• ...

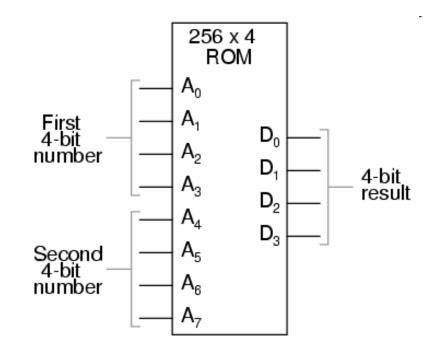

# EPROM as a Programmable Logic Device

ROMs are required for applications in which large amount of information needs to be stored in a nonvolatile manner. (Storage for microprocessor programs, fixed table of data, etc.) Another common application of the ROM is for the systematic realization of complex combinational circuits.

İzmir Institute of Technology

### FPGA Design

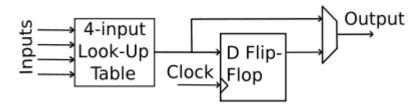

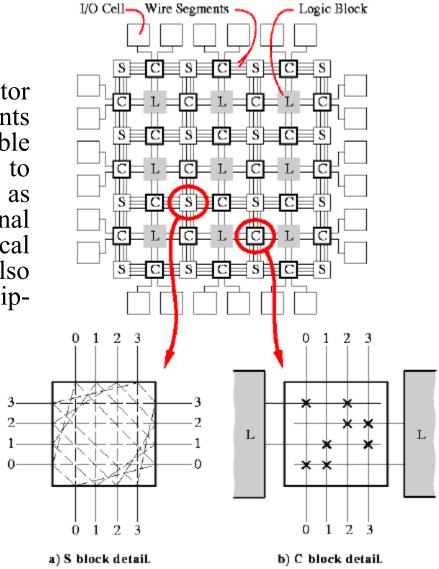

A field-programmable gate array is a semiconductor device containing programmable logic components called "logic blocks", and programmable interconnects. Logic blocks can be programmed to perform the function of basic logic gates such as AND, and XOR, or more complex combinational functions such as decoders or simple mathematical functions. In most FPGAs, the logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory.

A classic FPGA logic block consists of a 4-input lookup table (LUT), and a flip-flop:

#### **Soft Processors**

A soft microprocessor (also called softcore microprocessor or a soft processor) is a microprocessor core that can be wholly implemented using logic synthesis. It can be implemented via different semiconductor devices containing programmable logic (e.g., FPGA, CPLD).

Notable soft microprocessors include:

- •MicroBlaze

- Nios II

| Processor     | Developer             | Open Source | Bus Support   | Notes                                      | Project Home        |

|---------------|-----------------------|-------------|---------------|--------------------------------------------|---------------------|

| MicroBlaze    | Xilinx                | no          | OPB, FSL, LMB |                                            | Xilinx MicroBlaze ₺ |

| PicoBlaze     | Xilinx                | no          |               |                                            | Xilinx PicoBlaze ₺  |

| Nios, Nios II | Altera                | no          |               |                                            | Altera Nios II 🗗    |

| Cortex-M1     | Arm                   | no          |               |                                            | [1] 때               |

| Mico32        | Lattice               | yes         |               |                                            | LatticeMico32 년     |

| AEMB          | Shawn Tan             | yes         | Wishbone      | MicroBlaze EDK 3.2 compatible Verilog core | AEMB ₽              |

| OpenFire      | Virginia Tech CCM Lab | yes         | OPB, FSL      | Binary compatible with the MicroBlaze      | VT OpenFire ☎       |

| PacoBlaze     | Pablo Bleyer          | yes         |               | Compatible with the PicoBlaze processors   | PacoBlaze 🗗         |

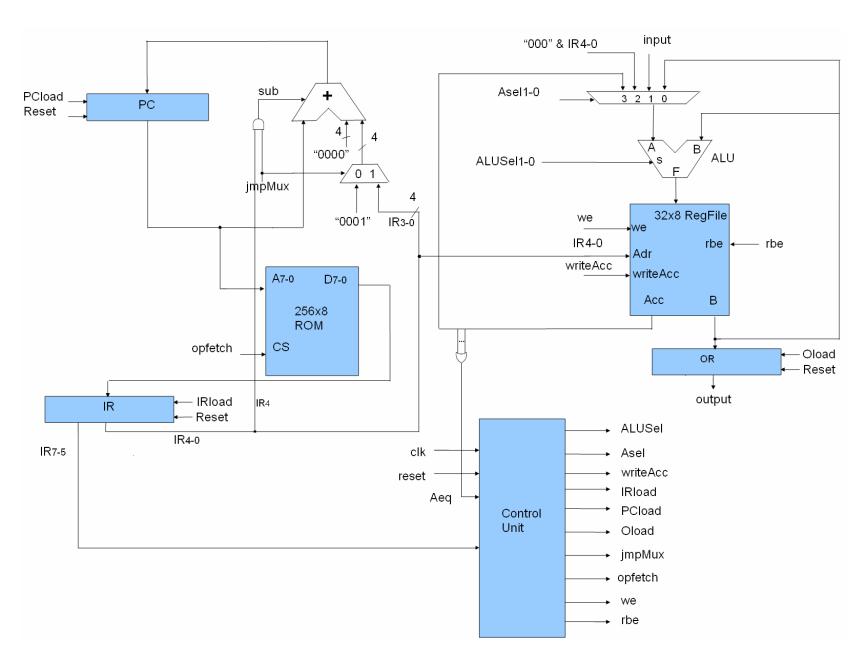

## $\mu P$ abs

#### Implementation in VHDL

```

23 library ieee;

use ieee std logic 1164 all:

use ieee std logic unsigned all:

use ieee numeric std all:

27

28

entity datapath is port(

29

in std logic;

30

reset:

in std logic;

31

input:

in std logic vector(7 downto 0);

output: out std logic vector(7 downto 0);

33

-- status signals

34

AeqO:

out std logic;

35

IROut:

out std logic vector (7 downto 5);

36

-- control signals

37

ALUSel:

in std logic vector(1 downto 0);

38

Asel:

in std logic vector(1 downto 0);

39

writeAcc: in std_logic;

40

IRload: in std logic;

41

PCload: in std logic;

42

Oload:

in std logic;

43

jmpMux:

in std logic;

44

opfetch: in std logic;

45

we:

in std logic;

rbe:

in std logic):

47

end datapath;

48

architecture imp of datapath is

50

51

signal dp ROMData, dp IR, dp IR2, dp ALU Out: std logic vector (7 downto 0);

signal dp PC, dp PCnext, dp Adder Out: std logic vector(7 downto 0);

signal dp_regfile_A, dp_regfile_B: std_logic_vector(7 downto 0);

54 signal dp mux4 Out: std logic vector(7 downto 0);

55 signal dp mux2 Out: std logic vector(3 downto 0);

signal dp mux2 Out8: std logic vector(7 downto 0);

signal f unsigned overflow: std logic;

signal sub jmp: std logic;

59

begin

Aeq0 \ll dp regfile A(0) or dp regfile A(1) or dp regfile A(2) or dp regfile A(3)

62

or dp regfile A(4) or dp regfile A(5) or dp regfile A(6) or dp regfile A(7);

dp IR2 <= "000" & dp IR(4 downto 0);

entity work.mux4 port map(Asel, dp regfile B, Input, dp IR2, dp regfile A, dp mux4 Out);

Instruction Register:entity work.IR port map(clk, reset, IRload, dp ROMData, dp IR);

66 ProgramCounter:

entity work.PC port map(clk, reset, PCload, dp PCnext, dp PC);

entity work.mux2 port map(jmpMux, "0001", dp IR(3 downto 0), dp mux2 Out);

dp mux2 Out8 <= "0000" & dp mux2 Out;

sub jmp <= jmpMux and dp IR(4);

Adder 8 bit:

entity work.addsub8 pc port map(dp PC, dp mux2 Out8, dp PCnext, sub jmp);

ProgramMemory:

entity work.rom 256 8 port map(opfetch, dp PC, dp ROMData);

RegisterFile:

entity work.regfile port map(clk, reset, we, writeAcc,

dp IR(4 downto 0), dp ALU Out, rbe, dp regfile A, dp regfile B);

74

ALU8:

entity work.ALU port map(ALUSel, dp mux4 Out, dp regfile B,

75

dp ALU Out, f unsigned overflow);

OutputRegister:

entity work.OReg port map(clk, reset, Oload, dp_regfile_B, output);

IROut <= dp IR(7 downto 5);</pre>

end imp;

```

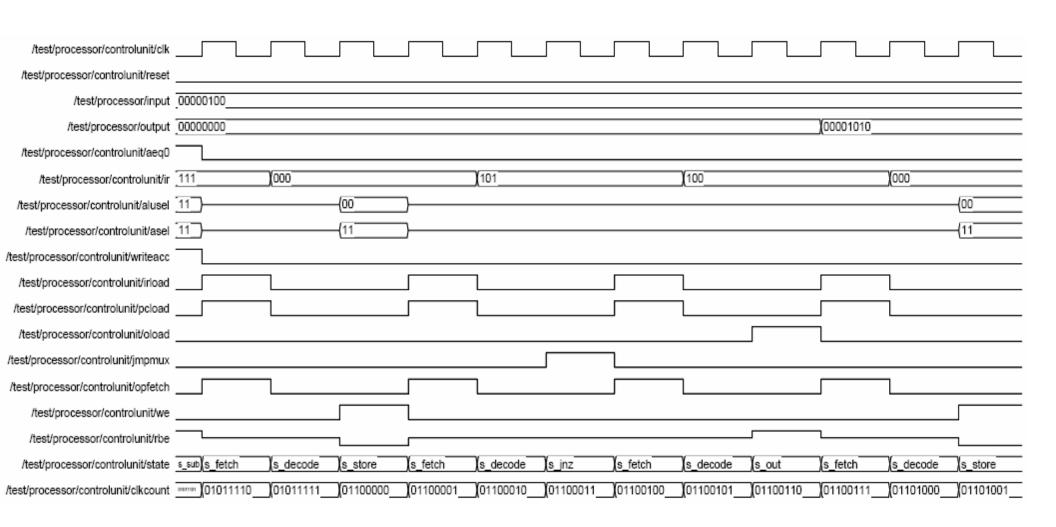

## Running the CPU

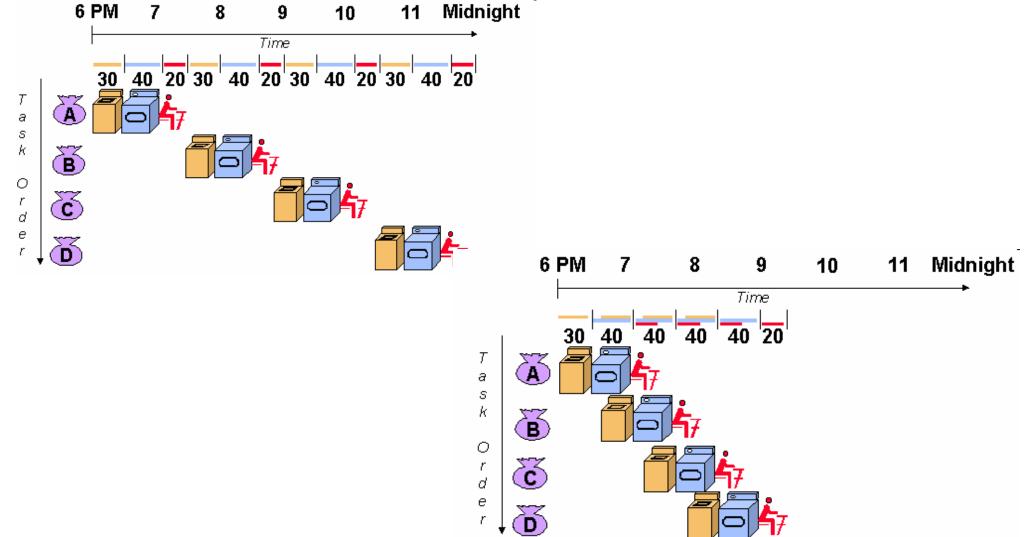

## Pipelining

| fetch | decode | execute |         |         |  |

|-------|--------|---------|---------|---------|--|

|       | fetch  | decode  | execute |         |  |

|       |        | fetch   | decode  | execute |  |