# CENG 311 Computer Architecture

### Lecture 4

Single and General Purpose µP Design

Design of the Components: Datapath and Control Unit

Asst. Prof. Tolga Ayav, Ph.D.

Department of Computer Engineering İzmir Institute of Technology

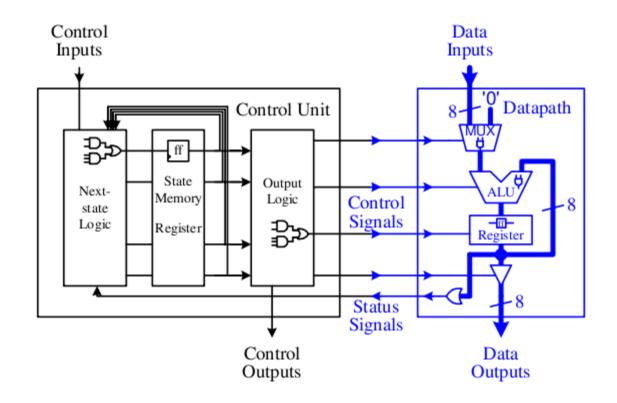

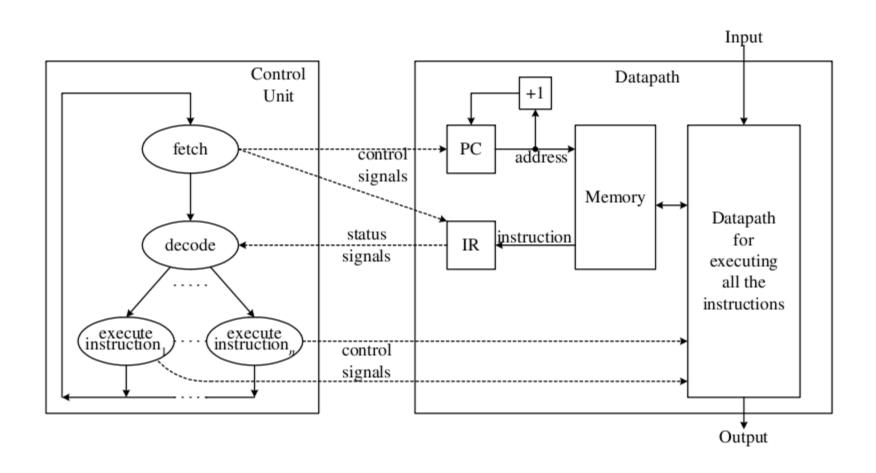

# General Structure of a Microprocessor

# Overview of CPU Design

# Datapath

- Manipuates data. It includes:

- Functional units: Adder, shifter, multiplier, ALU, comparator

- Registers and other memory elements for the temporary storage of the data

- Buses, multiplexers and tri-state buffers for the transfer of data between the different components in datapath and the external world.

# Why do we use datapath?

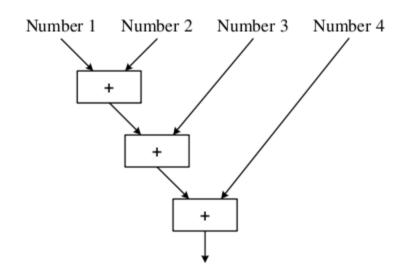

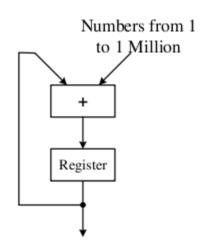

how do we design a circuit for performing more complex data operations or operations that involve multiple steps?

combinational circuit to add four numbers;

datapath to add one million numbers.

## **Designing Deticated Datapaths**

- What kind of registers to use, and how many are needed?

- What kind of functional units to use, and how many are needed?

- Can a certain functional unit be shared between two or more operations?

- How are the registers and functional units connected together so that all of the data movements specified by the algorithm can be realized?

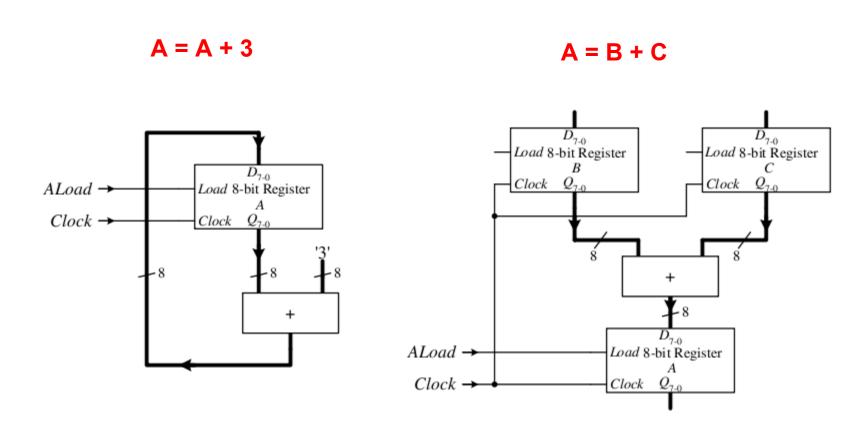

#### Two sample dedicated datapaths

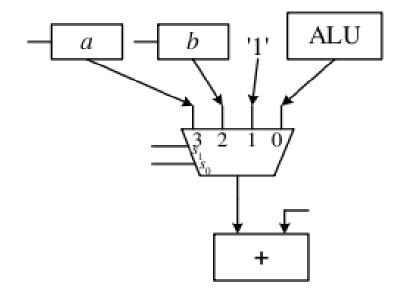

## Use of multiplexers

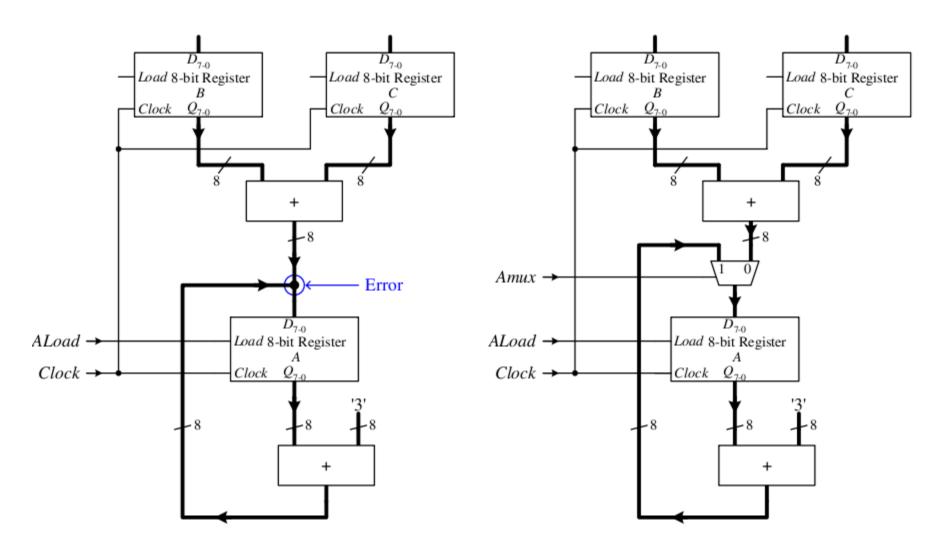

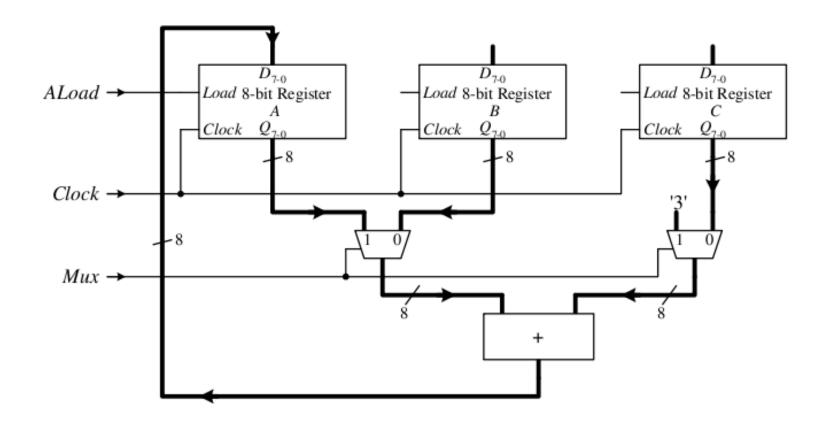

Datapath performing both A=A+3 and A=B+C (we use two adders).

İzmir Institute of Technology

Datapath performing both A=A+3 and A=B+C (we use only one adder).

### Data Transfer

Multiple destinations is not a problem. We can connect all of the destinations to the same source (Pay attention to the fan-out).

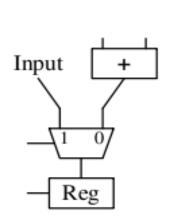

In case of multiple sources, multiplexers are used.

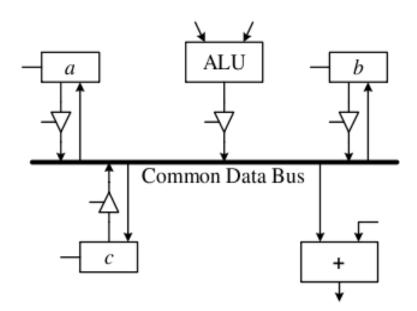

### **Tri-state Bus**

Another scheme where multiple sources and destinations can be connected to the same data bus is through the use of tri-state buffers.

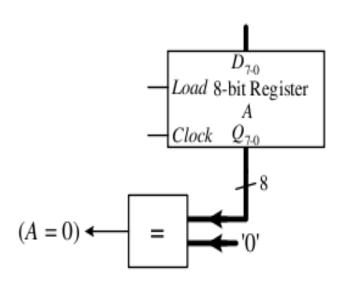

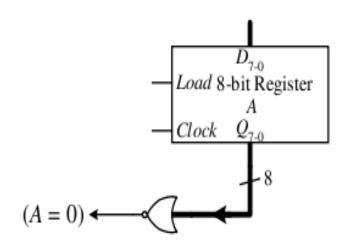

# Generating Status Signals

Status signals are the results of the conditional tests that the datapath supplies to the control unit.

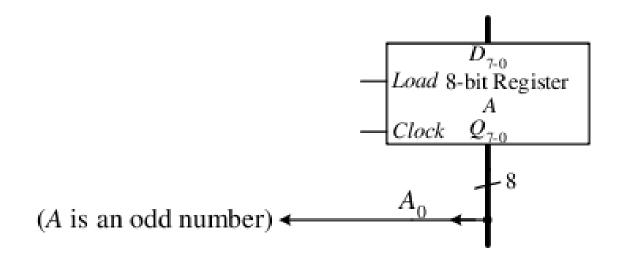

# Example: Generating Status Signals

IF (A is an odd number) THEN ...

İzmir Institute of Technology

# Examples of Dedicated Datapaths

- Simple if-then-else

- Counting 1 to 10

- Summation of n downto 1

- Factorial of n

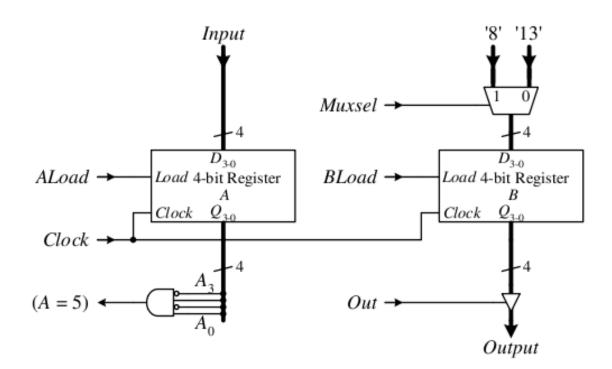

# Simple If-Then-Else

| 1 | INPUT A           |

|---|-------------------|

| 2 | IF $(A = 5)$ THEN |

| 3 | B = 8             |

| 4 | ELSE              |

| 5 | B = 13            |

| 6 | END IF            |

| 7 | OUTPUT B          |

| Control<br>Word | Instruction | ALoad | Muxsel | BLoad | Out |

|-----------------|-------------|-------|--------|-------|-----|

| 1               | INPUT A     | 1     | ×      | 0     | 0   |

| 2               | B = 8       | 0     | 1      | 1     | 0   |

| 3               | B = 13      | 0     | 0      | 1     | 0   |

| 4               | OUTPUT B    | 0     | ×      | 0     | 1   |

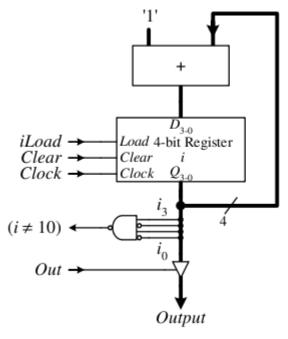

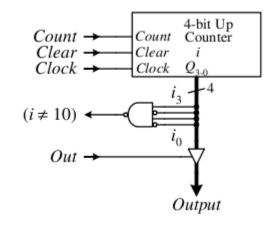

## Counting 1 to 10

| Control<br>Word | Instruction | iLoad | Clear | Out |

|-----------------|-------------|-------|-------|-----|

| 1               | i = 0       | 0     | 1     | 0   |

| 2               | i = i + 1   | 1     | 0     | 0   |

| 3               | OUTPUT i    | 0     | 0     | 1   |

| Control<br>Word | Instruction | Count | Clear | Out |

|-----------------|-------------|-------|-------|-----|

| 1               | i = 0       | 0     | 1     | 0   |

| 2               | i = i + 1   | 1     | 0     | 0   |

| 3               | OUTPUT i    | 0     | 0     | 1   |

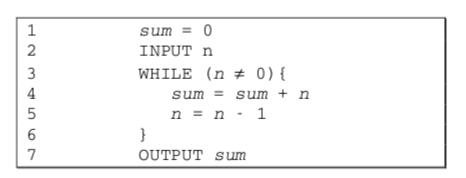

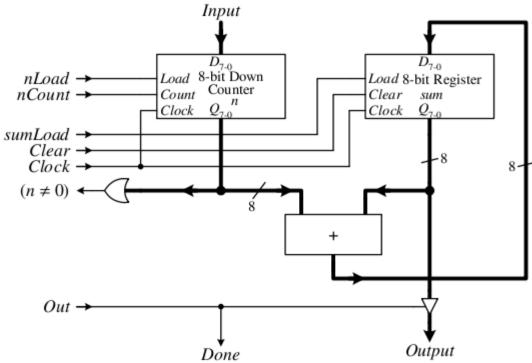

### Summation of *n* Downto 1

| Control<br>Word | Instruction   | nLoad | nCount | sumLoad | Clear | Out |

|-----------------|---------------|-------|--------|---------|-------|-----|

| 1               | sum = 0       | 0     | 0      | 0       | 1     | 0   |

| 2               | INPUT n       | 1     | 0      | 0       | 0     | 0   |

| 3               | sum = sum + n | 0     | 0      | 1       | 0     | 0   |

| 4               | n = n - 1     | 0     | 1      | 0       | 0     | 0   |

| 5               | OUTPUT sum    | 0     | 0      | 0       | 0     | 1   |

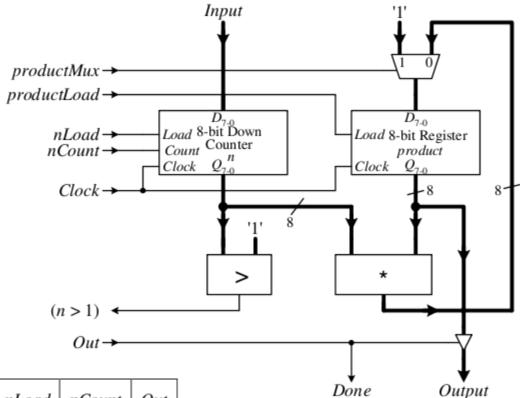

### Factorial of *n*

| Control<br>Word | Instruction           | productMux | productLoad | nLoad | nCount | Out |

|-----------------|-----------------------|------------|-------------|-------|--------|-----|

| 1               | INPUT n               | ×          | 0           | 1     | 0      | 0   |

| 2               | product = 1           | 1          | 1           | 0     | 0      | 0   |

| 3               | product = product * n | 0          | 1           | 0     | 0      | 0   |

| 4               | n = n - 1             | ×          | 0           | 0     | 1      | 0   |

| 5               | OUTPUT product        | ×          | 0           | 0     | 0      | 1   |

| Control<br>Word | Instruction                      | productMux | productLoad | nLoad | nCount | Out |

|-----------------|----------------------------------|------------|-------------|-------|--------|-----|

| 1               | INPUT $n$ , $product = 1$        | 1          | 1           | 1     | 0      | 0   |

| 2               | product = product * n, n = n - 1 | 0          | 1           | 0     | 1      | 0   |

| 3               | OUTPUT product                   | ×          | 0           | 0     | 0      | 1   |

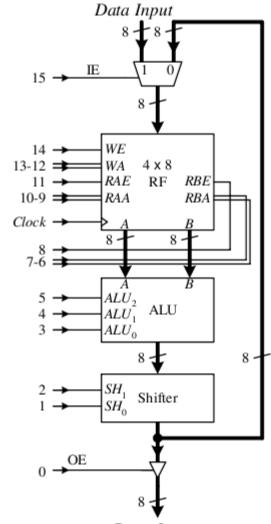

# General Purpose

| $ALU_2$ | $ALU_1$ | $ALU_0$ | Operation        |

|---------|---------|---------|------------------|

| 0       | 0       | 0       | Pass through A   |

| 0       | 0       | 1       | A and $B$        |

| 0       | 1       | 0       | $A 	ext{ or } B$ |

| 0       | 1       | 1       | NOT $A$          |

| 1       | 0       | 0       | A + B            |

| 1       | 0       | 1       | A - B            |

| 1       | 1       | 0       | A + 1            |

| 1       | 1       | 1       | A-1              |

| $SH_1$ | $SH_0$ | Operation                   |

|--------|--------|-----------------------------|

| 0      | 0      | Pass through                |

| 0      | 1      | Shift left and fill with 0  |

| 1      | 0      | Shift right and fill with 0 |

| 1      | 1      | Rotate right                |

Data Output

| Control | Instruction   | IE | WE | $WA_{1,0}$ | RAE | $RAA_{1,0}$ | RBE | $RBA_{1,0}$ | $ALU_{2,1,0}$   | $SH_{1,0}$ | OE |

|---------|---------------|----|----|------------|-----|-------------|-----|-------------|-----------------|------------|----|

| Word    | Histruction   | 15 | 14 | 13-12      | 11  | 10-9        | 8   | 7–6         | 5–3             | 2-1        | 0  |

| 1       | sum = 0       | 0  | 1  | 00         | 1   | 00          | 1   | 00          | 101 (subtract)  | 00         | 0  |

| 2       | INPUT n       | 1  | 1  | 01         | 0   | ××          | 0   | ××          | xxx             | ××         | 0  |

| 3       | sum = sum + n | 0  | 1  | 00         | 1   | 00          | 1   | 01          | 100 (add)       | 00         | 0  |

| 4       | n = n - 1     | 0  | 1  | 01         | 1   | 01          | 0   | ××          | 111 (decrement) | 00         | 0  |

| 5       | OUTPUT sum    | ×  | 0  | ××         | 1   | 00          | 0   | ××          | 000 (pass)      | 00         | 1  |

# Example: Write the control words for manipulating the above circuit to perform the following program

#### Multiplication of two unsigned numbers:

| Control | Instruction     | ΙE | WE | $W\!A_{1,0}$ | RAE | $RAA_{1,0}$ | RBE | $RBA_{1,0}$ | $ALU_{2,1,0}$   | $SH_{1,0}$ | OE |

|---------|-----------------|----|----|--------------|-----|-------------|-----|-------------|-----------------|------------|----|

| Word    | Instruction     | 15 | 14 | 13-12        | 11  | 10–9        | 8   | 7–6         | 5–3             | 2-1        | 0  |

| 1       | prod = 0        | 0  | 1  | 00           | 1   | 00          | 1   | 00          | 101 (subtract)  | 00         | 0  |

| 2       | INPUT A         | 1  | 1  | 01           | 0   | ××          | 0   | ××          | xxx             | ××         | 0  |

| 3       | INPUT B         | 1  | 1  | 10           | 0   | ××          | 0   | ××          | xxx             | ××         | 0  |

| 4       | prod = prod + A | 0  | 1  | 00           | 1   | 00          | 1   | 01          | 100 (add)       | 00         | 0  |

| 5       | B = B - 1       | 0  | 1  | 10           | 1   | 10          | 0   | ××          | 111 (decrement) | 00         | 0  |

| 6       | OUTPUT prod     | ×  | 0  | ××           | 1   | 00          | 0   | ××          | 000 (pass)      | 00         | 1  |

# VHDL for Datapath

### **16x8 RAM**

```

entity ram 16 8 is port(

in std logic; -- chip select

cs:

in std logic; -- write / read enable

wr:

in std logic vector(3 downto 0);

addr:

in std logic vector(7 downto 0); -- data in

di:

out std logic_vector(7 downto 0)); -- data out

do:

end ram 16 8;

architecture imp of ram 16 8 is

subtype cell is std logic vector(7 downto 0);

type ram type is array(0 to 15) of cell;

signal RAM:

ram type;

begin

process(cs, wr)

variable ctrl:

std_logic_vector(1 downto 0);

begin

ctrl := cs & wr;

case ctrl is

when "11" =>

RAM(conv integer(addr)) <= di;

do <= di;

when "10" =>

do <= RAM(conv integer(addr));</pre>

when others =>

do <= (others => 'Z');

end case;

end process;

end imp;

```

# 256x8 ROM (Program Memory)

```

entity rom 256 8 is port(

in std logic;

cs:

in std logic vector(7 downto 0);

addr:

out std logic vector(7 downto 0));

data:

end rom 256 8;

architecture imp of rom 256 8 is

subtype cell is std logic vector(7 downto 0);

type rom type is array(0 to 6) of cell;

constant ROM:

rom type :=(

inp & A,

dec & A,

outp & A,

jnz & "1011",

dec & A,

jnz & "1110",

nop);

begin

process (cs)

begin

if(cs = '1') then

data <= ROM(conv integer(addr));</pre>

else

data <= (others => 'Z');

end if;

end process;

end imp;

```

### 2 bit Multiplexer

### 4 bit Multiplexer

```

library ieee:

use ieee.std logic 1164.all;

use ieee.std logic unsigned.all;

use ieee.numeric std.all;

entity mux2 is port(

in std logic;

x0, x1: in std logic;

out std logic);

end mux2:

architecture imp of mux2 is

begin

process(s, x0, x1)

begin

if(s = '0') then

y \ll x0;

else

v \ll x1;

end if:

end process;

end imp;

```

```

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic unsigned.all;

use ieee.numeric std.all;

entity mux4 is port(

in std logic vector(1 downto 0);

x0, x1, x2, x3:

in std logic;

out std logic);

٧:

end mux4;

architecture imp of mux4 is

begin

process(S, x0, x1, x2, x3)

begin

case S is

when "00"

=> y <= x0;

=> y <= x1;

when "01"

when "10"

=> v <= x2;

=> y <= x3;

when "11"

=> V <= 'X';

when others

end case;

end process;

end imp;

```

## Register File

```

entity regfile is port(

clk:

in std logic;

in std logic;

reset:

-- reset

in std logic;

-- write enable

we:

in std logic vector(1 downto 0); -- write address (4 registers)

WA:

in std logic vector(7 downto 0); -- input

D:

in std logic;

rbe:

in std logic vector(1 downto 0); -- read address (4 registers)

RBA:

out std logic vector(7 downto 0);

portA:

out std logic vector(7 downto 0));

portB:

end regfile;

architecture imp of regfile is

subtype reg is std logic vector(7 downto 0);

type regArray is array(0 to 3) of reg;

signal RF: regArray;

begin

WritePort: Process(clk , reset)

begin

if(clk'event and clk='1') then

if(reset='1') then

RF(0) <= (others => '0'); -- register A (accumulator)

RF(1) <= (others => '0'); -- register B

RF(2) <= (others => '0'); -- register F (Flag)

RF(3) <= (others => '1'); -- register S (Stack Pointer)

elsif(we='1') then

RF(conv integer(WA)) <= D;

end if:

end if:

end process;

ReadPortB: Process(rbe, RBA)

begin

if(rbe='1') then

PortB <= RF(conv integer(RBA));

else

PortB <= (others => 'X');

end if;

end process;

ReadPortA: PortA <= RF(0); -- PortA always accumulator register

end imp;

```

## Instruction Register

```

entity IR is port(

clk:

in std logic;

in std logic;

reset:

-- reset

in std logic;

load:

in std_logic_vector(7 downto 0); -- input

INPUT :

OUTPUT:

out std_logic_vector(7 downto 0)); -- output

end IR;

architecture imp of IR is

subtype reg is std_logic_vector(7 downto 0);

signal IR8: reg;

begin

Process(clk , reset)

begin

if(clk'event and clk='1') then

if(reset='1') then

IR8 <= (others => '0');

elsif(load = '1') then

IR8 <= INPUT;</pre>

end if;

OUTPUT <= IR8;

end if:

end process;

end imp;

```

## Program Counter

```

entity PC is port(

clk:

in std logic;

in std logic;

reset:

-- reset

in std logic;

load:

INPUT :

in std logic vector(7 downto 0); -- input

OUTPUT:

out std logic_vector(7 downto 0)); -- output

end PC;

architecture imp of PC is

subtype reg is std_logic_vector(7 downto 0);

signal PC8: reg := "000000000";

begin

Process(clk , reset, load)

begin

if(clk'event and clk='1') then

if(reset='1') then

PC8 <= (others => '0');

elsif(load = '1') then

PC8 <= INPUT;

end if;

end if:

end process;

OUTPUT <= PC8;

end imp;

```

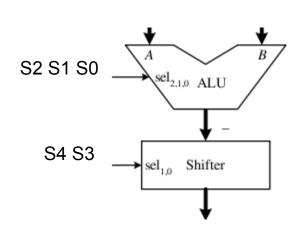

# Components of ALU

### **ALU** and Shifter

| s2 | s1 | s0 | Function         |

|----|----|----|------------------|

| 0  | 0  | 0  | Pass A to output |

| 0  | 0  | 1  | A and B          |

| 0  | 1  | 0  | A or B           |

| 0  | 1  | 1  | Α'               |

| 1  | 0  | 0  | A + B            |

| 1  | 0  | 1  | A – B            |

| 1  | 1  | 0  | A + 1            |

| 1  | 1  | 1  | A – 1            |

| s4 | s3 | Function                    |  |

|----|----|-----------------------------|--|

| 0  | 0  | Pass through                |  |

| 0  | 1  | Shift left and fill with 0  |  |

| 1  | 0  | Shift right and fill with 0 |  |

| 1  | 1  | Rotate right                |  |

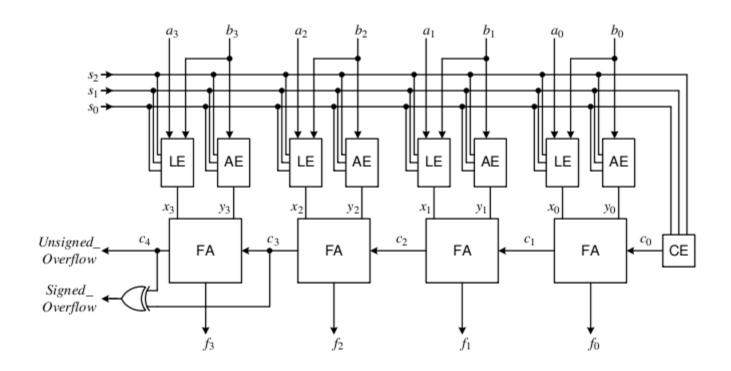

# Adder/Subtractor with Arithmetic and Logic Extenders

### Full Adder

# Arithmetic and Logic Extenders

| $s_2$ | $s_1$ | $s_0$ | Operation Name | Operation        | $x_i$ (LE)      | $y_i$ (AE) | c <sub>0</sub> (CE) |

|-------|-------|-------|----------------|------------------|-----------------|------------|---------------------|

| 0     | 0     | 0     | Pass           | Pass A to output | $a_i$           | 0          | 0                   |

| 0     | 0     | 1     | AND            | A  AND  B        | $a_i$ AND $b_i$ | 0          | 0                   |

| 0     | 1     | 0     | OR             | A OR B           | $a_i$ OR $b_i$  | 0          | 0                   |

| 0     | 1     | 1     | NOT            | A'               | $a_{i}{'}$      | 0          | 0                   |

| 1     | 0     | 0     | Addition       | A + B            | $a_i$           | $b_i$      | 0                   |

| 1     | 0     | 1     | Subtraction    | A-B              | $a_i$           | $b_i$      | 1                   |

| 1     | 1     | 0     | Increment      | A+1              | $a_i$           | 0          | 1                   |

| 1     | 1     | 1     | Decrement      | A-1              | $a_i$           | 1          | 0                   |

(a)

| $s_2$ | $s_1$ | $s_0$ | $\chi_i$    |

|-------|-------|-------|-------------|

| 0     | 0     | 0     | $a_i$       |

| 0     | 0     | 1     | $a_i b_i$   |

| 0     | 1     | 0     | $a_i + b_i$ |

| 0     | 1     | 1     | $a_{i}'$    |

| 1     | ×     | ×     | $a_i$       |

| $s_2$ | $s_1$ | $s_0$ | $b_i$ | $y_i$ |

|-------|-------|-------|-------|-------|

| 0     | ×     | ×     | ×     | 0     |

| 1     | 0     | 0     | 0     | 0     |

| 1     | 0     | 0     | 1     | 1     |

| 1     | 0     | 1     | 0     | 1     |

| 1     | 0     | 1     | 1     | 0     |

| 1     | 1     | 0     | 0     | 0     |

| 1     | 1     | 0     | 1     | 0     |

| 1     | 1     | 1     | 0     | 1     |

| 1     | 1     | 1     | 1     | 1     |

| $s_2$ | $s_1$  | $s_0$ | $c_0$ |

|-------|--------|-------|-------|

| 0     | ×      | ×     | 0     |

| 1     | 0<br>0 | 0     | 0     |

| 1     | 0      | 1     | 1     |

| 1     | 1      | 0     | 1     |

| 1     | 1      | 1     | 0     |

## Logic Extender

```

entity LE is port(

in std_logic_vector(2 downto 0);

in std_logic;

a, b:

out std logic);

x:

end LE;

architecture imp of LE is

begin

process(S, a, b)

begin

case S is

when "000" => x <= a;

when "001" => x <= a and b;

when "010" => x <= a or b;

when "011" => x <= not a;

when others => x <= a;

end case;

end process;

end imp;

```

### **Arithmetic Extender**

```

entity AE is port(

S:

in std_logic_vector(2 downto 0);

in std logic;

a, b:

out std logic);

end AE;

architecture imp of AE is

begin

process(S, a, b)

begin

case S is

when "100" => y <= b;

when "101" => y <= not b;

when "110" => y <= '0';

when "111" => y <= '1';

when others => y <= '0';

end case;

end process;

end imp;

```

### 8 bit LE

```

entity LE8 is port(

S:

in std logic vector(2 downto 0);

A, B:

in std logic vector(7 downto 0);

out std logic_vector(7 downto 0));

Χ:

end LE8;

architecture imp of LE8 is

component LE is port(

S:

in std logic vector(2 downto 0);

in std logic;

a, b:

out std logic);

x:

end component;

begin

U0: LE port map(S, A(0), B(0), X(0));

U1: LE port map(S, A(1), B(1), X(1));

U2: LE port map(S, A(2), B(2), X(2));

U3: LE port map(S, A(3), B(3), X(3));

U4: LE port map(S, A(4), B(4), X(4));

U5: LE port map(S, A(5), B(5), X(5));

U6: LE port map(S, A(6), B(6), X(6));

U7: LE port map(S, A(7), B(7), X(7));

end imp;

```

### 8 bit AE

```

entity AE8 is port(

in std_logic_vector(2 downto 0);

S:

in std logic vector(7 downto 0);

A, B:

Υ:

out std_logic_vector(7 downto 0));

end AE8;

architecture imp of AE8 is

component AE is port(

S:

in std_logic_vector(2 downto 0); --

in std logic;

a, b:

out std logic);

у:

end component;

begin

U0: AE port map(S, A(^{\circ}), B(^{\circ}), Y(^{\circ}));

U1: AE port map(S, A(1), B(1), Y(1));

U2: AE port map(S, A(2), B(2), Y(2));

U3: AE port map(S, A(3), B(3), Y(3));

U4: AE port map(S, A(4), B(4), Y(4));

U5: AE port map(S, A(5), B(5), Y(5));

U6: AE port map(S, A(6), B(6), Y(6));

U7: AE port map(S, A(7), B(7), Y(7));

end imp;

```

### addsub8

```

entity addsub8 is port(

in std logic vector(7 downto 0);

Α:

B:

in std logic vector(7 downto 0);

F:

out std logic vector(7 downto 0);

carryIn:

in std logic;

out std logic;

unsigned overflow:

out std logic);

signed overflow:

end addsub8;

architecture imp of addsub8 is

component FA port(

carryIn:

in std logic;

out std logic;

carryOut:

in std logic;

x, y:

out std logic);

s:

end component;

signal C:

std logic vector(7 downto 1);

begin

U0: FA port map(carryIn, C(1), A(0), B(0), F(0));

U1: FA port map(C(1), C(2), A(1), B(1), F(1));

U2: FA port map(C(2), C(3), A(2), B(2), F(2));

U3: FA port map(C(3), C(4), A(3), B(3), F(3));

U4: FA port map(C(4), C(5), A(4), B(4), F(4));

U5: FA port map(C(5), C(6), A(5), B(5), F(5));

U6: FA port map(C(6), C(7), A(6), B(6), F(6));

U7: FA port map(C(^{7}), unsigned overflow, A(^{7}), B(^{7}), F(^{7}));

signed overflow \leftarrow C(7) xor C(6);

end imp;

```

```

entity shifter8 is port(

S:

in std_logic_vector(1 downto 0);

in std logic vector(7 downto 0);

A:

Υ:

out std logic vector(7 downto 0);

carryOut:

out std logic;

out std logic);

zero:

end shifter8;

architecture imp of shifter8 is

component mux4 is port(

in std logic vector(1 downto 0);

S:

x0, x1, x2, x3: in std_logic;

out std logic);

end component;

begin

process(S) -- carry flag

begin

if(S="01") then

carryOut <= A(7);

elsif(S="10") then

carryOut <= A(0);

end if:

end process;

U0:

mux4 port map(S, A(0), '0', A(1), A(1), Y(0));

U1:

mux4 port map(S, A(1), A(0), A(2), A(2), Y(1));

U2:

mux4 port map(S, A(2), A(1), A(3), A(3), Y(2));

U3:

mux4 port map(S, A(3), A(2), A(4), A(4), Y(3));

U4:

mux4 port map(S, A(4), A(3), A(5), A(5), Y(4));

U5:

mux4 port map(S, A(5), A(4), A(6), A(6), Y(5));

U6:

mux4 port map(S, A(6), A(5), A(7), A(7), Y(6));

U7:

mux4 port map(S, A(7), A(6), '0', A(0), Y(7));

process(S) -- zero flag is set if the output of ALU is zero !! control the logic!

begin

if(S="00") then

if(A=0) then

zero <= '1';

else

zero <= '0';

end if:

end if:

end process;

end imp;

```

### Shifter

```

entity ALU is port(

in std_logic_vector(4 downto 0);

S:

A, B:

in std logic vector(7 downto 0);

out std logic vector(7 downto 0);

F:

out std logic;

unsigned overflow:

out std logic;

signed overflow:

out std logic;

carry:

out std logic);

zero:

end ALU:

architecture imp of ALU is

component LE8 is port(

S:

in std logic vector(2 downto 0); -- Selection bits

in std logic vector(7 downto 0);

A, B:

out std logic vector(7 downto 0));

Х:

end component;

component AE8 is port(

S:

in std logic vector(2 downto 0); -- Selection bits

A, B:

in std logic vector(7 downto 0);

out std logic vector(7 downto 0));

Υ:

end component;

component addsub8 is port(

in std logic vector(7 downto 0);

A:

В:

in std logic vector(7 downto 0);

out std logic vector(7 downto 0);

F:

in std logic;

carryIn:

out std logic;

unsigned overflow:

out std logic);

signed overflow:

end component;

component shifter8 is port(

S:

in std logic vector(1 downto 0);

in std logic vector(7 downto 0);

A:

out std logic vector(7 downto 0);

Υ:

carryOut:

out std logic;

out std logic);

zero:

end component;

signal X, Y, ShiftInput:

std logic vector(7 downto 0);

signal c0:

std logic;

begin

CarryExtender ALU: c0 \leftarrow (S(0) \text{ xor } S(1)) \text{ and } S(2);

LogicExtender8 ALU:

LE8 port map(S(2 downto 0), A, B, X);

ArithmeticExtender8 ALU: AE8 port map(S(2 downto 0), A, B, Y);

addsub8 port map(X, Y, ShiftInput, c0, unsigned overflow, signed overflow);

AddSub8 ALU:

Shifter8 ALU:

shifter8 port map(S(4 downto 3), ShiftInput, F, carry, zero);

end imp;

```

**ALU**